## STE - the Primary Validation Vehicle for **Processor Graphics FPU**

M, Achutha Kiran Kumar V Aarti Gupta; Rajnish Ghughal

CMI @ 9 Jan 2013

## STE - the Primary Validation Vehicle for **Processor Graphics FPU**

M, Achutha Kiran Kumar V Aarti Gupta Jr.; Rajnish Ghughal

# CMI @ 9 Jan 2013

### Purpose

- To demonstrate how STE validation methodology was effectively applied to validate a re-architected FPU in short runway GT project

- Demonstrate the effective utilization of formal methodology from the beginning of the project

- Next Gen GT FPU Val risk

- Results

- STE Overview

- GT STE implementation Challenges

- Conclusion

- Next Gen GT FPU Val risk

- Results

- STE Overview

- GT STE implementation Challenges

- Conclusion

# NextGenGT FPU Validation Challenges

| Activity                                                         | Challenge Posed                                                                           |

|------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Complete re-architecture of FPU                                  | Validate all uops within limited tim                                                      |

| RTL and C++ Checker concurrent development                       | Need an alternate validation methods<br>check the coded RTL                               |

| New Requirement: IEEE compliance for<br>precision and exceptions | Perfect methodology to check for<br>and ieee compliance similar to CPU<br>implementations |

| Increased scope of denormal handling for all precisions          | Dataspace explodes by 2X                                                                  |

| New FMA architecture                                             | To verify Sea of multipliers implem                                                       |

| Complex Programming capability                                   | Need to verify all permutations wind<br>increased data space                              |

#### neframe

### nodology to

# precision

### nentation

### ith

## Contemporary Methodologies at a glance

| Validation Technique | Methodology                                                                          |

|----------------------|--------------------------------------------------------------------------------------|

| DV#1                 | Dynamic validation of targeted interesting dataspace cases vectors generated by tool |

| DV#2                 | Dynamic validation of controlled random vector generation                            |

| DV#3                 | Dynamic validation using standard random test bench features of System Verilog       |

| FV#2                 | Formal Verification using a standard industrial tool                                 |

Need of the hour: A verification methodology that could meet the project timeline requirements

Solution: A Formal Verification Methodology suitable for proving Arithmetic circuits:

Symbolic Trajectory Evaluation (STE)

# **Reference Model** C++ based Ref model C++ based Ref model C++ based Ref model

#### C++ based specification

- BDWGT FPU Val risk

- Results

- STE Overview

- GT STE implementation Challenges

- Conclusion

# **Operation "FV Bug Hunt"**

What gave STE an edge over other verification methodologies in Next Gen GT?

- One Proof many projects

- One Proof Wider Coverage

- Proof ready before RTL and Fulsim

- Capability to mask unimplemented features

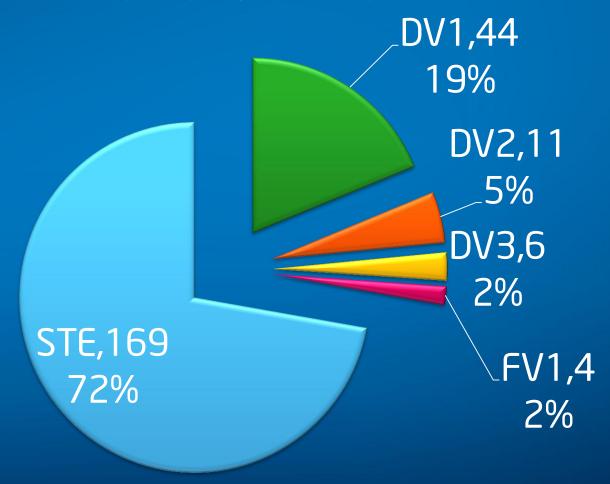

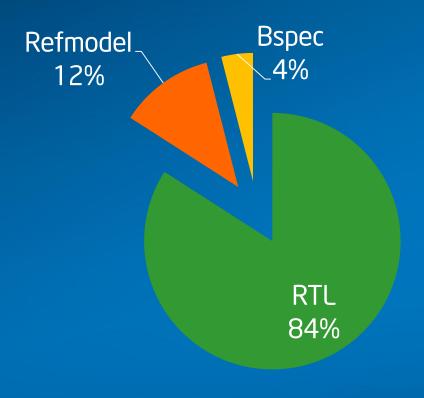

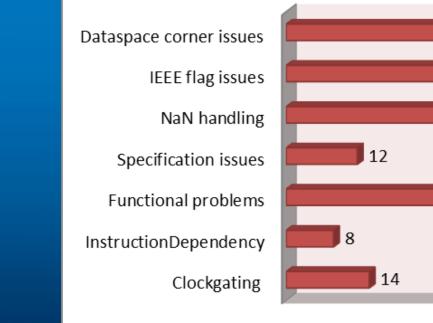

## **Bug Hunt Comparison**

RTL bugs caught by methodologies

## **Division of 201STE found bugs**

#### **Bug Division**

26

31

- BDWGT FPU Val risk

- Results

- STE Overview

- GT STE implementation Challenges

- Conclusion

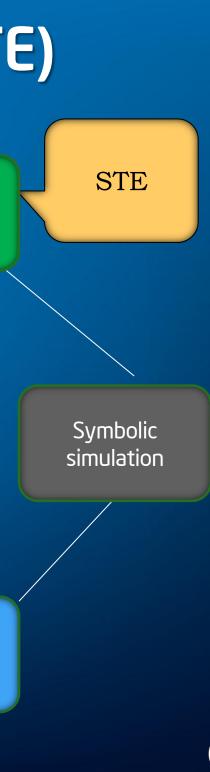

## Symbolic Trajectory Evaluation (STE)

- A hybrid between a symbolic simulator and a symbolic model checker

- Used primarily for checking designs

with large datapaths

Combines 3-valued simulation (0, 1, X) with symbolic simulation (using variables instead of fixed values) Symbolic three valued simulation

Three valued simulation

Standard Simulationbased verification

### **STE INFRASTRUCTURE**

Explored/Hang – Complexity reduction

Refine Antecedent/ Xs in circuit/ Complexity reduction

> BUG/Refine Consequent

IMPLEMENTATION PROVED!!

# **CVE - The Repository**

- CVE Common Verification Environment

- Collation of all proofs

- Foster reuse of common proofs across projects

- Avoid "reinventing the wheel" again and again

- Project specific qualifiers for differential treatment

- BDWGT FPU Val risk

- Results

- STE Overview

- GT STE implementation Challenges

- Conclusion

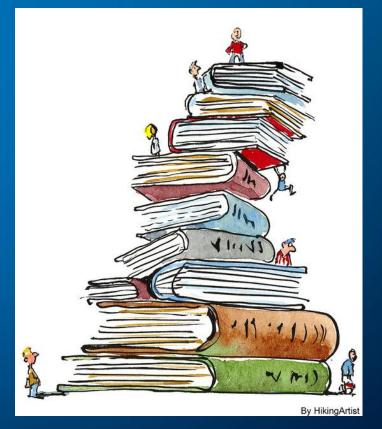

### STE Deployment Challenge

### GT STE Infrastructure

## An Exhaustive instruction format

• Gen graphics instruction set is compact but has a complex format

| [ <pred>]</pred>         | <instr></instr>         | <cond mod=""></cond>                                                                  |                                                        | ( <.sat >)           |

|--------------------------|-------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------|----------------------|

|                          | ( <execsize></execsize> | ) dst                                                                                 | {Accdst}                                               |                      |

| <srcmod></srcmod>        | src0                    | {Accsrc}                                                                              |                                                        |                      |

| <srcmod></srcmod>        | src1                    |                                                                                       |                                                        |                      |

| <srcmod></srcmod>        | SFCN                    |                                                                                       |                                                        |                      |

| CPU Instructio<br>Format | n                       | <in:< th=""><th>str&gt; <ex< th=""><th>cecsize&gt; dst src0src</th></ex<></th></in:<> | str> <ex< th=""><th>cecsize&gt; dst src0src</th></ex<> | cecsize> dst src0src |

|                          |                         |                                                                                       |                                                        |                      |

### **CPU infrastructure reuse challenges**

### GT's Own flag handling

Source Modification for all sources involved

### Saturation for Floats

Implicit/ Explicit Accumulator Source/Dest

#### Quadword

## **CPU** infrastructure reuse challenges

- Non uniform Denormal handling across precisions

- ALT Mode

- Different way of NaN Handling

- Instruction specific rounding modes

- HP and QW support

- New FMA Architecture / Implementation

# Our Approach

- Added / Redefined common functions/fields in CVE

- Project specific qualifiers

- New proofs

- Complexity reduction techniques

- New Variable ordering

- New Data type support

- Infrastructure to support new implementations

# Interesting bugs #1

#### (MAD-DP)

Multiplicand (a) = 0x1cc9 9398 0003 3273 =  $1.xyz * 2^{-512}$ Multiplier (b) =  $0x1ff4_04b2_5a15_c2bb = 1.abc * 2^{-563}$ Addend (c) =  $0x8000\ 0000\ 0000\ 0001 = 1.0 * 2^{(-1074)}$

Product  $(a * b) = 1.0 * 2^{(-1075)}$ Expected Result (ab+c)= 0x0000 0000 0000 0001 Actual Result (ab+c) = 0x0000 0000 0000 0000

### Dataspace Corner case issue

# Interesting bugs # 2

(MAD-DP)

**Conditions on preceding instruction:** Operation must be MAD-DP and Addend = Not INF/NAN/ZERO and Addend is -ve **Conditions on current Instruction: Operation is MUL-DP** Multiplicand/Multiplier = -ve NAN

# Instruction interaction bug

#### Expected Result= ffff ffff ffff ffff

#### Actual Result= 7fff ffff ffff ffff

### **Future Plans**

• STE on FPU for Future GT projects

• Apply STE on more datapath blocks..

Improve the proof database to add more uops

- BDWGT FPU Val risk

- Results

- STE Overview

- GT STE implementation Challenges

- Conclusion

## Conclusion

- Next Gen GT FPU re-architected for optimizations, IEEE compliance and for improved programmability

- STE as the prime tool found 201+ bugs

- Validation prior to Ref model readiness and wider coverage.

- Lower Time/uop validation

- Reduction in overall Validation cost for datapath dominated designs

## Acknowledgements

- Roope Kaivola FVCOE

- Tom Schubert CCDO FV Management

- Naveen Matam uarch for EU

- Maiyuran Subramanian Arch for EU

- Archana Vijaykumar, Durairaghavan Kasturirangan EU/Val Management